|

|

Vorlaufarbeiten und deren Technologiebasis

|

|

|

Die technologische und systemtechnische

Entwicklung der Mainframes war und ist ein besonderer "Hochtechnologiekomplex".

Hier focusierte sich der große Leistungswille, eine erfolgreiche

und wichtige Produktlinie weiterzuführen. Und hier trafen, neben der ohnehin extrem anspruchsvollen Materie,

in eklatanter Weise Widersprüche aufeinander, welche auch

renomierte westliche Firmen vorkomplizierte Aufgaben stellten

und z.B. wegen ihrer Komplexität zum Abbruch/ Auslauf

der SIEMENS- Mainframe - Linie in Augsburg im Zeitraum

1994/95 führten. Diese "Technologie" fordert halt

Höchstniveau!

Eine Mainframe muß eine "Zentraleinheit" sein

- nicht nur im Sprachgebrauch der 70er und 80er Jahre, sondern

sie steht in der System- Anwendungspyramide

im Spitzenbereich:

-

höchste Qualität- dh. technische

Verfügbarkeit ( d.h. extrem niedrige

Wahrscheinlichkeit eines Systemausfalles)

-

höchste Performance

-

Komfort und Qualität der Ausstattung

mit zuverlässiger Anwendungs- Software

-

Berechenbarkeit der Architektur

über 10 -15 Jahre für Großanwender

-

Rentabilität des Betriebes

Im Zeitraum nach 1995 war es nach Expertenbewertungen

zur Anwendungstechnik in der DDR (aber auch

international war das eindeutiger Trend ) notwendig, in den oberen

20% der Anwendungspyramide

eine ESER- Leistung von ca. 20-30 Mio OP/ps (MIPS) zu haben.

Der Spezifik der Arbeit am ESER- Hostkomplex ab ca. 1985

folgend sollen hier typische systemorientierte Technologie-

Aspekte kurz umrissen werden:

- die Komplexität der

IBM/ ESER- Architektur erfordert einen sehr aufwendigen

Spezial- Logikentwurf , dessen Prozessorkern(e) mit

höchster Packungsdichte realisiert sein muß/müssen (

wenige Dezi-Liter Volumen der Systemmoduln ), denn im

Bereich der geforderten MIPS ist die "Kupfer- Signallaufzeit"

vergleichbar mit den Schaltzeiten schneller Logikelemente

.

-

es bedarf schneller Logik

bei geringen Wärmeverlusteigenschaften -d.h.einer hohen

Integrationsfähigkeit, die architekturorientierten Eigenschaften

der VLSI- Basis (Strukturbreiten, Kontaktzahlen.. )

sollten "architektur-kompatibel" sein.

-

der Entwurf soll ein Minimum

an "sensiblen Zuverlässigkeits- Elementen"-

wie vor allem Kontakte, Lötstellen usw. besitzen.

-

die Bauelemente- Basis ( Halbleiter

und Bauelemente-Träger) soll wirtschaftlich vertretbare

Kosten haben.

-

unter den Bedingungen der

DDR- Wirtschaft musste das Konzept hochgradig aus Eigenaufkommen

( des RGW) produzierbar sein

In sehr komplizierten mehrjährigen Konzeptionsarbeiten

wurden mehrere Systemkonzepte einer ESER 4- Maschine (EC

1150) erarbeitet und mit den Hauptkooperationspartnern -

den Entwicklungsleitern des Kombinates Mikroelektronik -

beraten. Es wurden verschiedene Varianten mit Einsatz einer

Mischtechnologie (BiCMOS) , ECL und der CMOS- GateArray-

Linie U530/550 analysiert *). 1987 wurde dann die

CMOS- Gate- Array- Variante auf Basis

U5300/U5500 fixiert, verbunden

mit dem Einsatz eines keramischen Mehrschicht -Zwischenträgers

für die kompakte Montage von gehäuselosen Einzelchips (Multi-Chip-Modul)

der Größe 100x100 mm in der Vorzugsvariante. Unter bestimmten

Bedingungen ( geringere Leistung , Mehrkosten) wurden auch

Varianten ohne **) diesen (technologisch

und investitionsseitig kritischen) Zwischenträger analysiert.

*)

Dieser Prozess wurde sehr wohl immer mit Blick auf

die Bilanzbarkeit der Schaltkreisbasis unter DDR-

Bedingungen geführt. Eine sehr enge Zusammenarbeit

mit den führenden Spezialisten im Zentrum für

Mikroelektronik Dresden (ZMD) des Kombinates Zeiss

Jena machte das möglich, wir waren immer im

"aktuellen Kanal" der Technologieentwicklungen und

damit sowohl modern, als auch "bilanzierbar".

**)

Eine Anmerkung aus Sicht eines

Besuchers der Informatikabteilung des Deutschen Museums

München : Dort war der "TCM100" von IBM ausgestellt,

der in IBM /308X- Systemen zum Einsatz kam. Dessen enormer

Technologieaufwand, von der grünen "schrumpfungsfreien"

Keramik, über Leiterzugpasten höchster Qualität bis

zu supergenauen Verbindungen von 36 Lagen über 36 000

Kontaktlöcher und neuartigen Kugel-Bond-Technologien

für 132 Chips mit je 120 Kontakten machten dem Autor

2006 bei einem Besuch in München augenscheinlich, dass

sein Auftrag aus dem Jahre 1988 , eine Alternativvariante

für EC 1150 ohne den keramischen

Mehrschicht -Zwischenträger zu konzipieren, sicher "lebensnotwenig"

geworden wäre... . unter DDR- Bedingungen und bei Konfrontation

mit der 32-Bit Linie in Dresdner, deren Entwickler

derartige Lösungen beim Vorbild ja nicht kannten..

Der

Schaltkreisentwurf wurde zum

integralen Bestandteil des Logikentwurfes des FG Geräte

E2 bzw. des WTZ des Buchungsmaschinenwerkes (später

Ascota-AG Chemnitz),d.h. das eigene Arbeitsfeld des Logikentwurfes

wanderte folgerichtig mit dem technologischen Fortschritt

in den Bereich der Mikroelektronik- Technologie. Das Fachgebiet

E2 erarbeitete sich die Fähigkeiten, Schaltkreisentwürfe

im Komplex des Gesamtlogikentwurfes der ZE zu erarbeiten,

dh. incl. der Logiksimulation, Prüfpatternerstellung usw..

Eine neue Qualität der Entwurfssicherheit war die notwendige

Konsequenz und es wurde lebensnotwendig, den Entwurf einer

sicheren logischen und technischen Simulation zu unterziehen.

Die ersten 3 LSI- Gate Arrays U5300 wurden so erfolgreich für den Personal-

Computer EC 1835 (PC/AT 2. Generation) entworfen. Das Fachgebiet

hatte sich auf die Anforderungen der Verwertung von U5300/U5500

in seinem selbstentwickelten Entwurfssystem eingestellt

und war hier auf die 90er Jahre gut vorbereitet mit einer

sehr flexibel nutzbaren Technologie für ESER- Mainframes

, Personalcomputer oder im Prinzip sogar zusätzlich zum

ESER auch für DEC-VAX - Logikentwürfe.(

Letzteres allerdings ging weit über die Vorstellungswelt

der Dresdner Kollegen hinaus).

Unser Konzept war es, mit der CMOS- Schaltkreisbasis

U5500 mit ihrer höheren Intergrationsdichte und

Geschwindigkeit den Weg in die 90er Jahre zu sichern. Für

1990 waren U5500- Gate Arrays mit ca. 50

T.Gatern /Chip geplant. Die Entwicklungskonzepte sahen

vor:

|

|

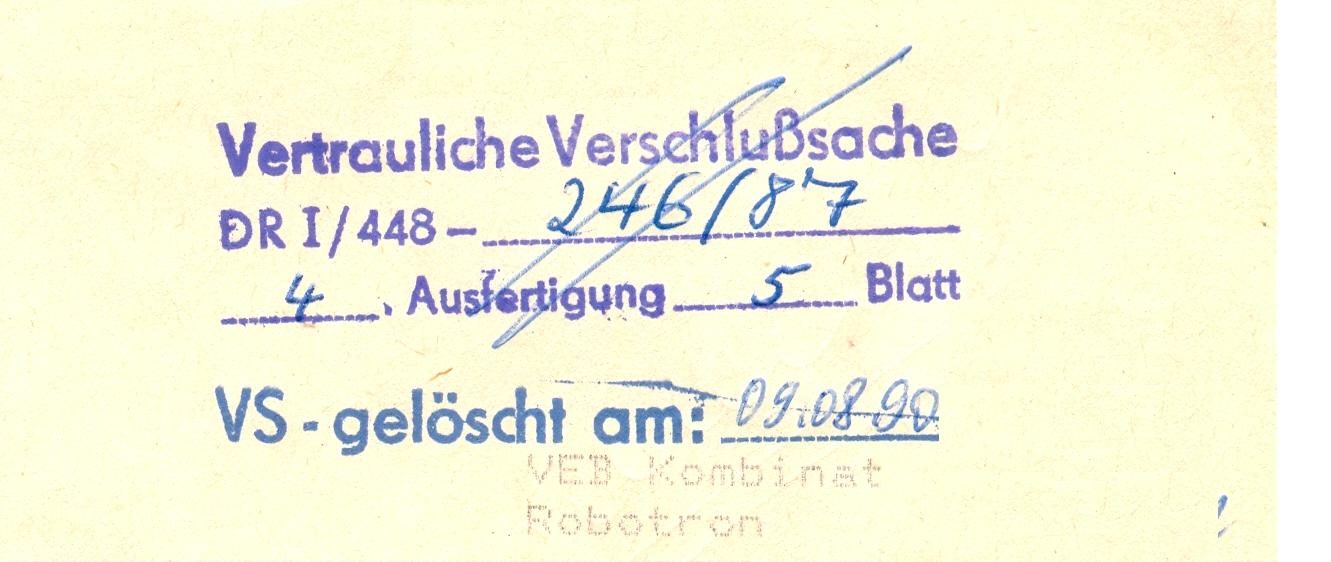

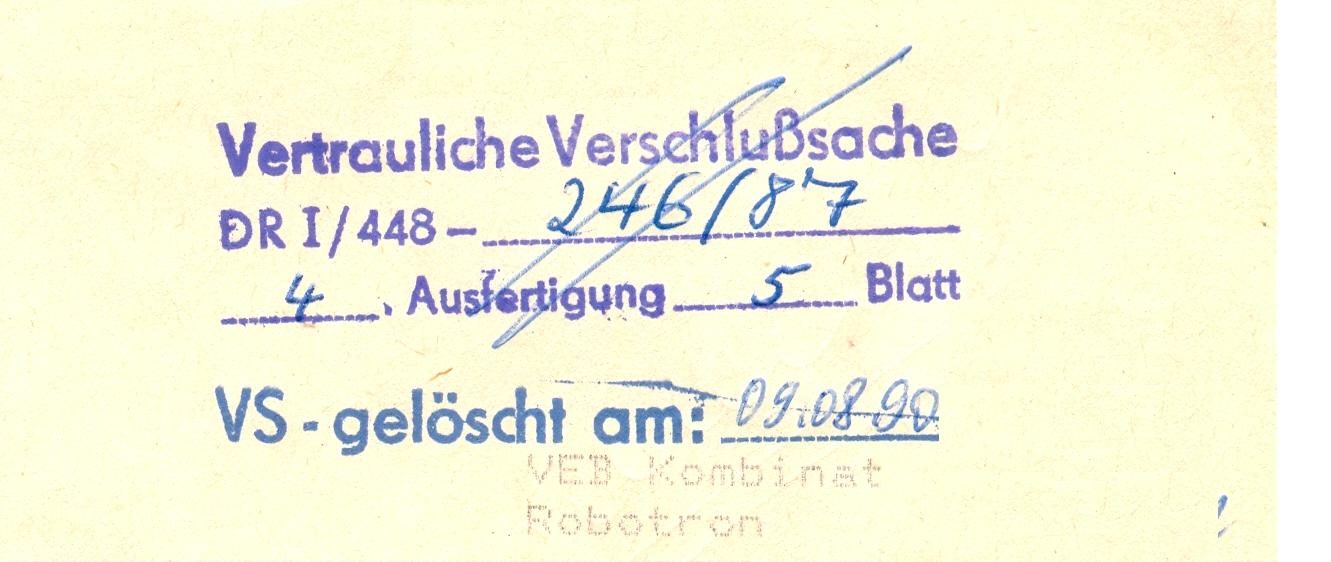

Mehrere Auszüge aus

Original- Unterlagen dieser Zeit

sind noch verfügbar und unterstreichen das o. Gesagt deutlich.

Die Position der Rechentechnik im internationalen Vergleich

und ihre technologische Abhängigkeit vom Stand der Bauelementebasis

und Basiskonstruktion war allen an den Systemstrategien

beteiligten sehr wohl bewusst !>Dynamik

der Architekturen

,

In

der o.g.

Unterlage

"

Dynamik der Architekturen"

kann der Betrachter heute noch sehr genau die Härte

des Ringens um Entwicklungstempo und -Qualität gegenüber

dem Weltmarkt einerseits , aber auch gegenüber den UdSSR

- Plänen und nicht zuletzt gegenüber dem Dresdner "

DEC VAX- Nachbau" als Hauptkonkurrenten nachvollziehen.

Der Vergleich der EC 1150M mit 6 Jahren "Rückstand"

zum IBM- Vergleich gegenüber einem Rückstand von 9 Jahren

bei der 32-bit- Linie gegenüber DEC VAX 8800 spricht

sehr deutlich für sich.

Hier Auszuege

aus erhaltenen Unterlagen :

Wie man sieht, hatte sich das ESER- Systemmanagement des

Fachgebietes Geräte nicht nur mit Widrigkeiten besonderer

Art auseinanderzusetzen, sondern es gelang

-

viele wichtige Entscheidungen

zu gestalten und

-

eine große Entwicklungseinheit

von ca. 1000 engagierten Leuten noch 1989 mit unseren

technischen Zielen zu motivieren,

Wir sprachen damals im

Hause (weitgehend) offen

und ehrlich über die Realitäten und

erläuterten unsere Strategie deutlich und

für die Mitarbeiter weitgehend nachvollziehbar.

Ein Vergleich

zum damaligen Stand in der UdSSR zeigte uns einen gewissen

theoretischen "Vorsprung". Verglichen mit den

Entwicklungstendenzen in der UdSSR lagen wir 1988/89 mit

den ESER- Arbeiten mit gutem Kurs im Fahrwasser der Entwicklungen

- unter RGW- Bedingungen! Die enge Zusammenarbeit

mit den CMOS- Teams des ZMD Dresden(zum VEB Kombinat Carl

Zeiss Jena gehörig) bestärkte uns dabei.

Die Darlegungen

des ESER-Generalkontrukteurs V.V. Prschijalkowskij nach

dem Zusammenbruch des ESER bestätigen uns das. Es ist heute

insbesondere für Insider interessant, noch einmal

die Auszüge zu lesen , die wir dazu beim Generalkonstrukteur

finden > "

UEBERBLICK ESER_VVPr "

und "

Geschichte des NIZEWT (bis 2003)

".

" Unter diesen Bedingungen schwierigster Finanzlage und

des Wegganges von Spezialisten konnte der Bereich 16

trotzdem die Entwicklungsarbeiten an der ЕС-1181 und

ЕС-1195 abschließen. Die ЕС-1181 (Chefkonstrukteur

Chramzow, I.S. ) - das letzte ESER- Modell ЕС ЭВМ für

universellen Einsatz wurde gemeinsam mit der Minsker

Produktionsvereinigung für Rechentechnik (МПО ВТ )

bearbeitet. Dank der Matrix- LSI- SK I -300

, die letztendlich doch durch das Selenograder Werk

"Mikron" geliefert wurden, hatte sie ausgezeichnete

technische Daten."

|

|

Bemerkungen

zur ESER- PC- Linie:

Wie bereits dargestellt, wurde 1987 die CMOS- Gate- Array-

Technologie für unser „ESER 4“- Projekt ausgewählt

und auf Basis der Schaltkreise U 5300/U 5500 im Hause festgeschrieben.

Die Logik-Entwurfsarbeiten und Verfahren im Fachgebiet wurden

folglich auf Verfahren unmittelbar für den Schaltkreisentwurf

erweitert. Das gab die Möglichkeit, den aus volkswirtschaftlicher

Sicht zunehmenden Anteil der Wertschöpfung für Schaltkreis-

Entwurf durch eigene Kapazitäten mitzutragen und bei Planungen

weitgehend unabhängig und schnell zu sein. Auch neue Entwurfstechnik

mußte dafür installiert werden. Das Haus platzte aus allen

Nähten!

Der erste produktwirksame Schritt auf dem Wege zu LSI-Schaltkreisen,

den unser Haus anteilig selbst bearbeitete, waren

CMOS- Gate- Arrays für den PC EC 1835. Ergänzend zu den

Basisschaltkreisen der U 80286 (Intel/80286)-Familie,

geplant bzw. gefertigt aus

dem Kombinat Mikroelektronik Erfurt wurde im PC EC 1835

eine Vielzahl von Logik- Bauteilen des IBM/AT durch

drei Typen Gate- Arrays ersetzt. Sie waren im Fachgebiet

Geräte entworfen und 1989 im VEB Zentrum für Mikroelektronik

Dresden für unsere Funktionsmuster gefertigt worden.

Dieser IBM/AT-kompatible- EC1835 war voll

funktionsafähig und stellte im ESER eine echte Spitzenleistung

dar- 1989!!

Das PC- Knowhow in Chemnitz und Sömmerda ermöglichte auch

nach der DM-Einführung umfangreiche Exporte in die UdSSR

und bot weitere Chancen.

Vielfach wurde und wird heute noch im Zusammenhang mit der

Robotron- Geschichte die Frage gestellt, ob die Zuordnung

des ESER- Mainframe Entwicklungszentrums (E2) zum Buchungsmaschinenwerk

Karl- Marx- Stadt (BWK) nicht automatisch die Aufgabe der

ESER- Mainframe- Linie bedeutete, denn das BWK-Profil lag

ja bei PC, Terminals, Floppy- Disc und weiteren Gross- Serien-

Produkten. Die wichtigste Antwort darauf war 1989 und weit

nach 1990 in Chemnitz, bildlich gesprochen, als großer Beton-

Rohbau zu sehen, das Gebäude des geplanten

Zentrums für die Endfertigung von

CMOS- Schaltkreisen. Heute ist davon noch die Baugrube

in der Nähe der Gleise am Hauptbahnhof zu sehen.

In Karl- Marx- Stadt, der Werkzeug- und Textilmaschinen

-Hochburg der DDR bestand generell ein LSI -

Mangel, der nicht ständig durch- teilweise

Embargo-behinderte NSW- Importe tragbar war.

Im Zusammenhang damit und der gewählten Orientierung auf CMOS

Gate- Arrays wurde im Bezirk Karl- Marx- Stadt eine Kooperation

der dort starken Zweige des Textilmaschinenbaus und Werkzeugmaschinenbaus

und unter Mitwirkung der TU Karl- Marx- Stadt unter

deren Rektor Prof. Manfred Kraus vorbereitet. Unter

Verantwortung von TEXTIMA wurde der Bau eines

Zentrums für die Endfertigung der kundenspezifischen Ebenen

von CMOS- Schaltkreisen als Komplexvorhaben unter

unserer Mitwirkung geplant und mit dessen Bau begonnen,

seine Kapazitäten wurden neben dem kompletten regionalen

Bedarf auch für den gesamten ESER- Bedarf für PC + Mainframes

(ESER IV) ausgelegt.

Auch diese Fakten stellen eine gewisse Bestätigung für die

Wahl unserer Strategien dar.

|

|

Den unerwartet schnellen

Zusammenbruch des RGW hatten 1988/1989 nicht

einmal die Strategen des Weißen Hauses oder gar des Bundeskanzleramtes

vorausgesehen. Die FG E2 - Leitung rund um den ESER- CK

trafen diese Ereignisse mit dieser extremen Dynamik

natürlich völlig unerwartet....Es ging nur

noch darum, maximal

dafür zu arbeiten, möglichst vielen Mitarbeitern

eine Perspektive, d.h. die Basis für ein weiteres (zweites)

Berufsleben zu sichern!

Als unverrückbarer

Fakt steht fest: man

kann über Architekturen fabulieren oder sie nüchtern auf

einer soliden konstruktiv- technologischen Basis umsetzten.

Heute wissen wir genauer, dass die UdSSR- Entwicklungen

mit ihrer schwachen zivilen Mikroelektronik- Basis dem DDR-

Rechentechnik- Export sicher noch weitere Chancen eröffnet

hätten .. . Aber, wie der ESER- Generalkonstrukteur so lakonisch

formulierte , .. das einst so stolze ESER- System zerfiel

unter dem Sturm der historischen Ereignisse.

Was bleibt ist für viele E2-

Mitstreiter ein gewisser Stolz

auf ein interessantes Lebenswerk und für viele 1990 noch

jüngeren Kolleginnen und Kollegen eine gute Chance in einem "zweiten

professionellen" Leben.

|

|

© Dr.Jungnickel

|